What factors are related to the yield of semiconductor chips?

Apr 10, 2026

Leave a message

So, what is this yield related to? Generally speaking, it is mainly related to the following factors:

Production process

The production process includes production conditions (plant, equipment, materials), process level, process experience and management. The production process of wafers is very complex, the entire tape-out process includes hundreds or even thousands of steps such as lithography, etching, chemical vapor deposition, physical vapor deposition, ion implantation and furnace tubes, which need to enter different machines once or multiple times, which is much more complicated than the process of meat buns! At each step, it is possible to import defects. So the question is, when customers choose the wafer fab and process, how to know whether the wafer fab is good or not, the process is stable and unstable, how to estimate the yield and cost of their products? In fact, the fab will provide the customer with a DO value (average defect density) to characterize the yield level of the process. Based on this Do value and specific calculation formulas (different fabs may provide different calculation formulas), the approximate yield of the product can be predicted in advance.

Sounds amazing, doesn't it? So what is this Do? How to predict yield? In fact, DO is to characterize the probability of defects per unit area of the wafer. The derivation of DO is very complex. But we can simplify this concept to understand what it is, for example, a meat bun will sandwich 100 diced meat, and out of 100 diced meat, there will be 1 diced meat that is spoiled. We consider this defect density as 0.01 (1%). In another store, 10 of the same 100 diced meat will be spoiled, so the defect density is relatively 0.1 (10%). So which bun is good? Of course, 0.01 is better than 0.1. Generally speaking, the smaller the DO, the more mature the process and the higher the yield.

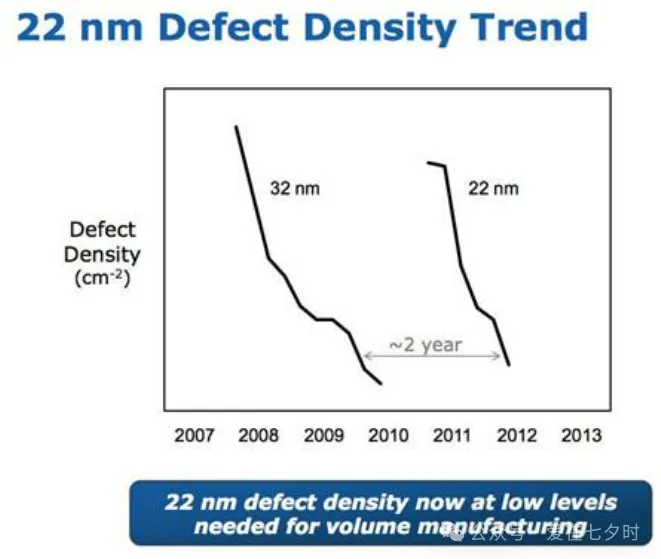

Of course, fabs will continue to improve and improve their processes, and DO will generally decrease in the two-year process from the beginning of R&D to mature mass production. Let's take a look at the D0 development trend of the 32nm and 22nm processes.

The question is, is yield only related to DO? No, no, no! Let's go back to the bun, one of the 100 diced meat is bad. If we cut 100 servings and the bad diced meat affects one serving, then the yield rate is 99%. What if we cut 1000 buns? Then the bad diced meat still only affects one serving, but the yield rate becomes 99.9% at this time. We think of each part as a chip, so the larger the area of the chip, the lower the yield. In fact, to put it more popularly, this is the same as the fact that fat people are more likely to be shot than thin people in war. See the following diagram on the relationship between DO, chip area, and yield:

Is this the end of the story about the magical DO? Not yet, everyone should pay attention to the fact that DO is different for the Logic (logic) circuit and SRAM (static memory) circuit in the chip! Why? Because the density of SRAM is much larger than that of Logic, then the same defect may fall in the open space, and if it falls in the SRAM area, it is likely to affect the circuit. Therefore, fabs provide different DO values for Logic and SRAM, and when predicting the target yield, it is necessary to comprehensively consider the area ratio of SRAM and Logic in the chip. Just imagine, if a stone falls from the sky, where are the casualties heavier?

2,Product design methodology

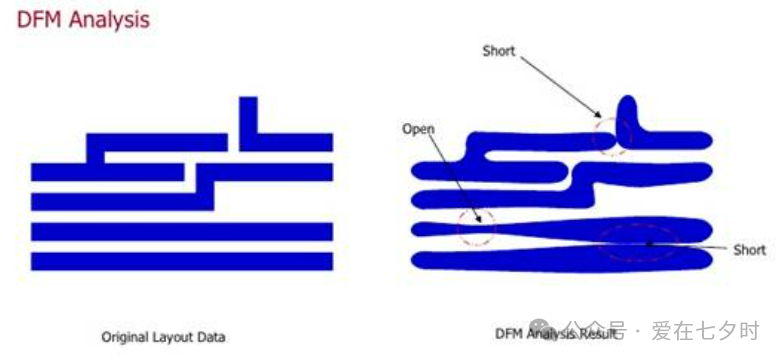

We are talking about manufacturability design issues. The design methods mentioned here are mainly related to design for manufacturability (DFM) and design for testability (DFT). Manufacturability, as the name suggests, is to take into account manufacturing factors when designing. For the same design, different drawing methods, component placement directions, and positions may affect the final yield. This is an inevitable problem brought about when the process becomes more advanced and the line width becomes smaller and smaller.

Typically, when the process enters 65nm and below, the fab will provide manufacturability design rules for IC design companies to check. However, it is generally believed that the manufacturability design rules for 65nm and 45nm processes are for reference. Because the process is mature enough, it is not necessary to spend a lot of effort on the design to comply with the design rules of manufacturability. But at 28nm and below, the manufacturability rule must be strictly adhered to during the design process.

DFT is more complicated, so I won't go into detail here to avoid confusing everyone.

3,Test methodology

Test Technology & Management. First of all, it should be emphasized that the test method will not change the quality of the chip itself, and will not turn a chip with a failed function into a good chip because of different test methods. However, optimized testing methods can control costs while maintaining high test coverage, reduce DPPM (Defective Parts Per Million) and reduce return rates at end customers.

After the wafer is produced, it undergoes an electrical test called the Wafer Acceptance Test (WAT) before leaving the fab. This test tests the electrical performance of the test key on the scribe line. Test keys are typically designed with a variety of components, such as NMOS, PMOS, resistors, capacitors, and other process-related characteristics of different sizes. This can be regarded as a primary election. Wafers that have serious production problems that cause the electrical performance of the test key to exceed specifications will be screened out and scrapped in this process. This scrapped wafer, because it has not yet been shipped to the customer, does not charge the customer money and is absorbed by the wafer factory itself.

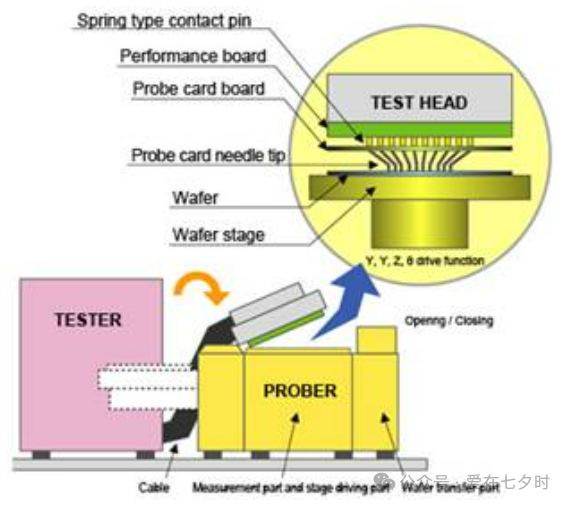

After the WAT test is completed, the wafer process is completed. The next step is to come to the test plant for testing. The first pre-wafer cutting test is called CP (Chip Probing) because this test is tested on a complete wafer, and the machine used is called a prober. Each product will have a prober card designed for itself, on which the corresponding test probes and circuits are connected to the test bench according to the position of the chip's test pad. During each test, the test head is pressed down from above, and the probe is inserted into the pad, and then power is supplied for testing.

Speaking of which, we have to mention the cost of testing. Normally, we will find that the cost of testing an IC product accounts for a large part of the overall cost. Therefore, how to optimize the test program to be simple and efficient (to achieve the necessary test coverage) is the job of the test engineer of the IC design company. The more simplified the test procedure, the shorter the test time required and the lower the test cost.

Generally, in the CP stage, in order to save costs, the function of all chips will not be measured. For example, some simulation functional tests that require expensive test machines may be omitted in the CP stage and placed in the FT (Final Test) later. In addition to optimizing the test program, the optimization of the test method is also the direction that everyone is working. The following methods are generally used to reduce the cost of CP testing:

After a period of production, the low-yield chips at the edge of the wafer are directly ignored and not adopted.

Generally, after we get a certain amount of CP test results for a product, we can stack the results. Wafer periphery, incomplete chips or low-yield chips that are affected by being too close to the edges, are removed directly on the test program.

If the incomplete chips and low-yield chips in the above figure are deleted, each wafer can be tested 12 chips less, which reduces the cost and relatively improves the yield and quality and quality.

2,So can the optimized test map above be optimized? We know that the same probe card can measure several chips at the same time, and how to arrange them is a problem. If 6 can be measured at the same time, then whether the arrangement is 2x3 or 3x2, or 1x6 will affect the number of needle insertions; Different needle walking methods will also produce different needle pricking times. For example, it is possible that the second picture below may be a few fewer needle than the first picture, which will save testing time. There is now specialized software on the market that can simulate and optimize these.

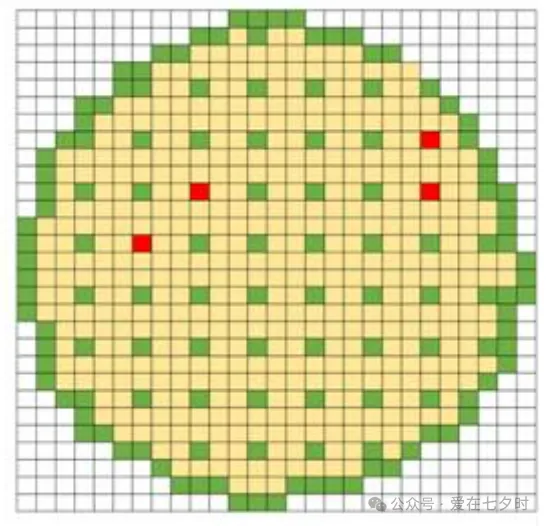

3,Sampling testing: When there are thousands or even tens of thousands of chips on a wafer, and the yield has reached a stable height, many companies use sampling testing in the CP stage to reduce the test time. In the image below, yellow represents chips that are not tested, and green represents chips that need to be tested. The figure below is a typical sampling method. Please note that the yield of one turn on the edge of the wafer is relatively low, and this full test is sometimes considered during sampling.

There are also chips that only measure the outside and center of the wafer with the lowest yield. For example:

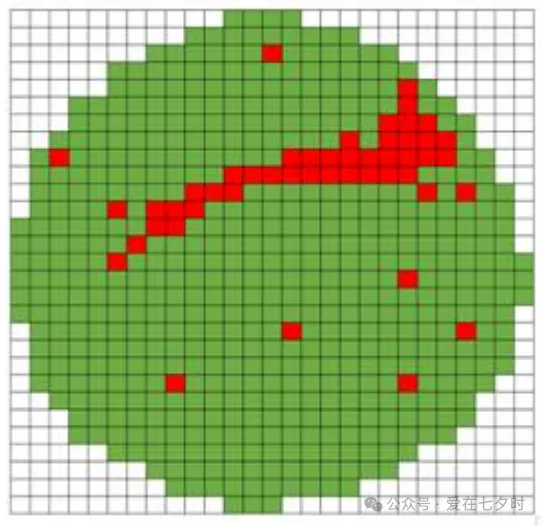

No matter how it changes, there is only one goal, that is, to screen out as many unqualified chips as possible with the least testing cost, so the question is, will the above sampling miss some abnormally low yield wafers, resulting in the waste of subsequent packaging and final testing? The answer is yes. Sampling is definitely riskier than full testing. Take the following figure as an example: Suppose the following figure is the sampling result, green represents the good chip, and red represents the failed chip. It seems that only four bad chips were detected, and the yield rate is not bad.

However, if a full test is performed, it may not only miss a low-yield chip, but also cause potential reliability issues due to this omission:

So, how to avoid the above problems as much as possible in the case of random testing? Some big data real-time monitoring software can monitor and control the needle movement while testing, and the tester can set a condition in advance, for example, when a point fails, the test probe automatically tests whether the chip around the failed chip is a good chip. If the surroundings are good, then the probe returns to the next sampling point to continue sampling. If there is still something bad in the surrounding chip, continue to test around the failed chip. Then we will find that as shown in the figure below, this failed chip has been measured. For reliability reasons, the tester can decide whether to scrap the good chip in a circle around this failed chip.

Having said all this, the first chip test of CP has just ended. The chip tested by CP will go through the process of crystal back polishing, cutting and other procedures to remove the failed chip and send the good chip to the packaging process. In the packaging process, the chip will also have a certain yield loss when it goes through high-temperature and high-pressure processes such as wire punching and die-stamping, but this part is very small and stable in the absence of accidents, and is generally not considered much. However, in recent years, some companies are considering using big data to monitor the parameters of packaging machines and conduct big data analysis to improve packaging yield, which will not be discussed here.

When the packaging is completed, the chip will look good.

After that, the packaged chip enters the final test. Because the final test is the last test of many IC product manufacturers on their products, this test will be relatively more complete than the CP test, and the final test can do the high-speed and mix-signal test that CP cannot do.

The yield rate of the final test, because it has been screened through the previous layers, is generally good. However, as we said, because the final test contains more items than CP, it may also encounter low yield problems. Under normal circumstances, the low yield of the final test is more difficult to find the cause and more complicated. It may be related to simulation parameters, may be related to packaging, and may be related to ESD failure, so various failure analysis methods are often used.

For many companies, after the product reaches the final test, it can be shipped to customers. However, some companies or products will also do system-level testing (SLT, System leveltest, also known as bench test) after the final test. SLT is to build a real system application environment for testing. Taking mobile phone chips as an example, you can build an openphone simulation customer prototype for chip testing, and even simulate various problems that customers may encounter in use, such as mobile phone signal directionality problems and battery low temperature protection problems. These tests were not possible in the previous CP and FT. Of course, SLT is more time-consuming, so it can be conducted in the form of regular random testing.

Send Inquiry